Milestones:SPARC RISC Architecture, 1987

- Date Dedicated

- 2015/02/13

- Dedication #

- 153

- Location

- Santa Clara, California, U.S.A.

- IEEE Regions

- 6

- IEEE sections

- Santa Clara Valley

- Achievement date range

- 1987

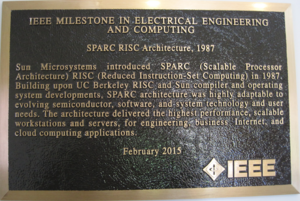

Title

SPARC RISC Architecture, 1987

Citation

Sun Microsystems introduced SPARC (Scalable Processor Architecture) RISC (Reduced Instruction-Set Computing) in 1987. Building upon UC Berkeley RISC and Sun compiler and operating system developments, SPARC architecture was highly adaptable to evolving semiconductor, software, and system technology and user needs. The architecture delivered the highest performance, scalable workstations and servers, for engineering, business, Internet, and cloud computing applications.

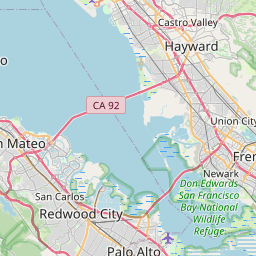

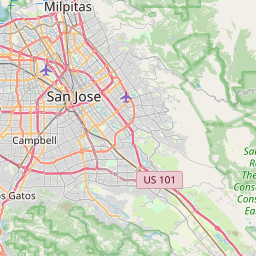

Street address(es) and GPS coordinates of the Milestone Plaque Sites

- Site 1: Clock Tower Building (Oracle campus), 4040 Palm Dr., Santa Clara, CA 95054 US (GPS: 37.393577, -121.953407)

- Site 2: Computer History Museum, 1401 N. Shoreline Blvd, Mountain View, CA 94043 US, (GPS: 37.414757, -122.077679)

Details of the physical location of the plaque

- Site 1: In the front lobby of the historic Clock Tower Building on the Oracle campus.

- Site 2: On the inside face of the front patio brick wall, near the museum's Main Entrance.

How the plaque site is protected/secured

- Site 1: The building is publicly-accessible; the Oracle campus is secured, and is protected as a historical site.

- Site 2: Building security; 24/7 access.

Historical significance of the work

The SPARC RISC CPU architecture provided the following:

- a popular platform for semiconductor IC design and development

- a new level of performance that enabled a myriad of new applications

- a cost-effective technology made available to commercial uses in volume

- an open architecture adapted by multiple companies allowing independent innovations

- a standardized architecture: IEEE 1754-1994 "IEEE Standard for a 32-bit Microprocessor Architecture"

- backward compatibility

- compiler, OS and SPARC architecture and systems evolved together to provide differentiated performance

- pioneered the fabless semiconductor microprocessor manufacturing process

Obstacles (technical, political, geographic) that needed to be overcome

- initial funding constraints

- finding semiconductor partners to fab the CPUs

- concurrent development of CPU, OS, Compiler

- porting of software to new SPARC architecture

- dislodging of the incumbent 68000 architecture

Features that set this work apart from similar achievements

- delivered performance

- optimized for delivering total system solutions (OS, Compiler, CPU, Systems)

- maniacal focus on SPARC systems: "all wood behind one arrow"

- differentiated from other RISC architectures, including MIPS, POWER, PA-RISC

Significant references

- IEEE 1754-1994 "IEEE Standard for a 32-bit Microprocessor Architecture"

- SPARC Wikipedia Page

- Computer History Museum SPARC Microprocessor Oral History 1: Origin and Evolution

- Computer History Museum SPARC Microprocessor Oral History 2: Business Development

- Computer History Museum Oral History: Scott McNealy

- Computer History Museum Oral History: Wayne Rosing

Supporting materials

- Media:SPARC_Timeline.pdf

- Media:1987 Computer system news 10MIPs.pdf

- Media:1987 March 10 San Jose Mercury News - Unisys-Sun lic.pdf

- Media:1987 Oct Wall Street Journal - Xerox-SPARC lic.pdf

- Media:1988 - LSI mfg.pdf

- SPARC: A Scalable Processor Architecture (this paper cites 8 IEEE publications)

Blog Postings

IEEE Presents Prestigious SPARC Milestone Plaque in Front of SRO Crowd (archive.org link)

Oracle to Receive IEEE Milestone Award for SPARC RISC Architecture

Highlights from the above blog:

A History of Record Performance and Mission Critical Enterprise Capabilities

Sun Microsystems first introduced SPARC (Scalable Processor Architecture) RISC (Reduced Instruction-Set Computing) in 1987. Over the course of its life, the SPARC processor architecture has powered millions of servers and workstations, and is still a leading and highly valued technology today.

Closely integrated with the Oracle Solaris operating system, Oracle's SPARC-based systems provide customers extreme performance to maximize the up-time and ROI of mission-critical enterprise applications and cloud services—at a fraction of the cost of mainframe computers. With a long history of record-breaking performance, SPARC-based systems have achieved over 450 record benchmarks, with 32 currently standing. Today, the SPARC processor family is used in Oracle's enterprise servers to create architectures that are optimized for a powerful mix of applications, from CRM systems and Java/Web middleware infrastructure applications to mission-critical ERP and backend OLTP/data warehousing enterprise applications that depend on high availability and scalability.

SPARC Innovations Continue

Building on over 27 years of innovations and a long list of "firsts," Oracle continues to engineer record-breaking SPARC-based systems running Oracle Solaris. As first announced at Hot Chips 2014, Oracle’s new and revolutionary Software in Silicon technology hardwires key software processes directly onto the processor. Software in Silicon accelerates functions running on special engines on the processor's silicon, separate from its cores, and speeds up application performance while retaining the overall functionality of the processor.

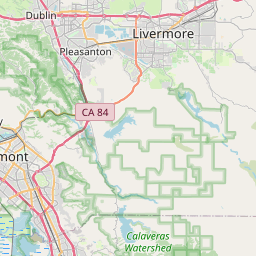

Map