## **Bus Structures**

## MODULE TEST

You may wish to review the exercises or audio-visual material before taking this module test. Once you begin the test, do not refer to the course materials.

1. For each statement below, write a T in the space provided if the statement correctly describes a bus structure. Write an F in the

There are six questions.

| space provided if the statement does not correctly structure.                            | describe a bus |

|------------------------------------------------------------------------------------------|----------------|

| A Bus Structure                                                                          | T or F         |

| is a cable containing a bundle of wires.                                                 |                |

| is a group of cables each containing a single transmission wire.                         |                |

| provides communication paths between<br>the CPU, main memory, and peripheral<br>devices. |                |

| can transmit any combination of addresses and data on each of its wires.                 | _              |

| can pass information about data, control signals, and addresses.                         |                |

|                                                                                          |                |

includes address, data, and control lines.

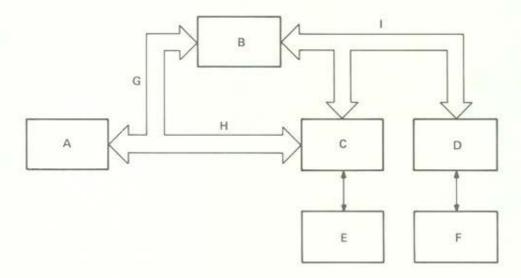

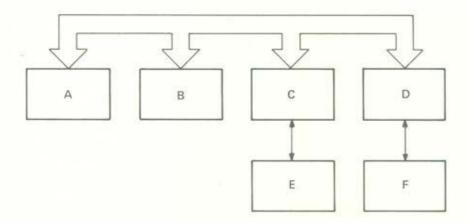

- 2. Block diagrams of single-bus and 3-bus configurations are given below. A list of components and bus types is also given. Match each component with its position in the diagrams by writing the correct letter in the space provided. Also, match each bus type in the 3-bus configuration by writing the correct letter in the space provided.

- a. 3-Bus Configuration

b. Single-Bus Configuration

| J.  | 3-Bus Configuration      |                     |  |

|-----|--------------------------|---------------------|--|

|     | Components               | Position in Diagram |  |

|     | Disk Interface           |                     |  |

|     | Terminal                 |                     |  |

|     | CPU                      | V                   |  |

|     | Terminal Interface       |                     |  |

|     | Moving Head Disk         |                     |  |

|     | Main Memory              |                     |  |

|     | Bus Types                |                     |  |

|     | DMA                      |                     |  |

|     | 1/0                      |                     |  |

|     | Memory                   |                     |  |

| 11, | Single-Bus Configuration |                     |  |

|     | Components               | Position in Diagram |  |

|     | Disk Interface           |                     |  |

|     | Moving Head Disk         |                     |  |

|     | CPU                      |                     |  |

|     | Terminal Interface       |                     |  |

|     | Main Memory              |                     |  |

|     | Tarminal                 |                     |  |

3. For each statement, indicate whether it refers to a single-bus (SB) or 3-bus (3B) configuration by writing the correct abbreviation in the blank space.

| Statement                                                                                                                     | Bus Type |

|-------------------------------------------------------------------------------------------------------------------------------|----------|

| More versatile data flow.                                                                                                     |          |

| Larger maximum memory size.                                                                                                   |          |

| More potential for throughput if multi-<br>ported memory is used.                                                             |          |

| Fewer machine instructions for program-<br>mer to remember.                                                                   |          |

| <ol> <li>Indicate whether each of the statements be<br/>false information about DMA by writing eithe<br/>provided.</li> </ol> |          |

| DMA                                                                                                                           | T or F   |

| means "data and memory access."                                                                                               |          |

| means "direct memory addressing."                                                                                             |          |

| means "direct memory access."                                                                                                 |          |

| refers to busses, interfaces, and devices.                                                                                    |          |

| refers to busses only.                                                                                                        |          |

| moves information to and from main memory via the CPU.                                                                        | _        |

| moves information to and from main memory without passing through CPU.                                                        | _        |

- - a. Serial Transmission

b. Parallel Transmission

6. The six functions of a typical interface and their descriptions are given below. Match each function with its description.

| Function          | Description |

|-------------------|-------------|

| Control           |             |

| Buffer            |             |

| Status            |             |

| Conversion        |             |

| Housekeeping      |             |

| Program Interrupt |             |

## Descriptions

- Performs specialized functions, such as updating a byte counter or current address register.

- b. Monitors the operational situation of the peripheral and stores the information as data. This data, such as READY and ERROR, can be acted on when the CPU is temporarily halted.

- Serves as a compensator for differences in the speeds of peripherals and the rest of the computer system.

- d. Governs the operation of the peripheral based on command information supplied by the software.

- e. Performs required data changes (e.g., serial to parallel) so that data can be transferred between the peripheral and CPU correctly.

- f. Halts a CPU whenever a peripheral requires some type of action from the software.