File:OMNI-spec.pdf 29.03.13 / Vg

Remo Vogelsang 7/26/71

# OMNIBUS SPECIFICATION (Preliminary)

# Contents:

- 1. Scope

- 2. General Electrical Characteristic

- 3. The Various Groups of Signal Lines

- 3.1 Group Definition

- 3.2 Line Characteristics

- 3.3 Terminators and Pull-Up Resistors

- 3.4 Drivers and Driving Capability

- 3.5 Receivers and Loading Characteristic

- 3.6 Noise Margins

- 4. Timing Considerations

- Crosstalk

Chapter 9 of the "PDP8/E Small Computer Handbook 1971" provides a fairly extensive description of all the aspects of the OMNIBUS. The paragraphs "Bus Specifications, Loading Rules, and Electrical Considerations of Driving a Line" provide some basic information of the electrical characteristics of the OMNIBUS. However, a detailed description of these properties would be beyond the scope of the Small Computer Handbook.

It is the purpose of this specification to provide a detailed description of the electrical characteristic of the OMNIBUS. It is most important for designers dealing with the OMNIBUS to become familiar with all the aspects and peculiarities of the OMNIBUS.

2. General Electrical Characteristic

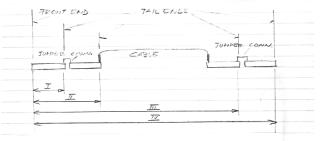

2.1 The Various Length of the OMNIBUS

Various system configurations call for four different lengths of the OMNIBUS as indicated by the sketch below. Most of the electrical characteristics of the bus change accordingly. Any standard piece of hardware shall be designed, so it will operate properly under worst case conditions in any length bus. Acceptance criterias of hardware have to be based on any length bus, too.

2.2 Mechanical and Electrical Properties

|                           | Length | Prop. Delaytime | Capacitance to Gnd. |

|---------------------------|--------|-----------------|---------------------|

|                           | (inch) | Typ. (ns)       | Typ. (pF)           |

| OMNIBUS I " II " III " IV | 10     | 6               | 70                  |

|                           | 23     | 12              | 140                 |

|                           | 71     | 24              | 530                 |

|                           | 84     | 30              | 600                 |

Characteristic impedance  $\mathbf{Z}_{0}$ : 100 ohm typ.

- 4 -

3. The Various Groups of Signal Lines

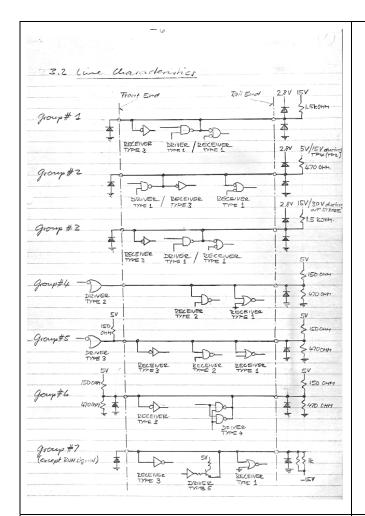

Different functions on an OMNIBUS line call for different electrical characteristics of drivers, receivers, terminators, etc. The electrical characteristic can be best described by breaking down the 96 signal lines into seven distinct groups (refer also to "Bus Load" schematic E-CS-M32 $\beta$ - $\beta$ -1).

3.1 Group Definition

3.1.1 Group #1: Signal lines for open collector drivers.

List: MDØØ ... MDll INT ROST MEM START SKIP LINK BRK IN PROG LINK DATA IND 1 IND 2 OVERFLOW LD ADD ENABLE INTERNAL I/O MA, MS LOAD CONT BREAK DATA CONT NOT LAST XFER F SET BREAK CYCLE STOP RES Ø KEY CONTROL SW СØ IRØ IRl IR2 CPMA DISABLE USER MODE

3.1.2 Group #2: Signal lines for open collector drivers and  $\underline{\text{fast}}$  speed up during TP2 or TP4 respectively.

List: MAØØ ... MAI1

EMAØ

EMAI

EMA2

ROM ADDRESS

MS IR DISABLE

F

D

E

MD DIR

Speed up at TP4

3.1.3 Group #3: Signal lines for open collector drivers and <u>slow</u> speed up during INT STROBE.

List: DATA ØØ ... DATA 11 INT IN PROGRESS

3.1.4 Group #4: Memory timing & control signal lines.

List: RETURN SOURCE STROBE WRITE INHIBIT

Group #5: General timing signal lines terminated at one end.

List: TP1 ... TP4

TS1 ... TS4

INT STROBE

I/O PAUSE (not a timing signal by definition, however the loading conditions are similar as for timing signals).

3.1.6 Group #6: General timing signal lines terminated at both ends.

List: LINK LOAD

BUS STROBE

3.1.7 Group #7: Miscellaneous

List: RUN (special treatment necessary because of power on/off peculiarities)

POWER OK (low state has to be guaranteed with no power)

- 5 -

3.3 Terminators and Pull-Up Resistors

- 3.3.1 Section 3.2 reflects the hardware used for terminators and pull-up resistors of the various groups of lines. Each group has its own tailored set of clamp diodes terminator resistors, pull-up resistors according to driving capability, thresholds of receivers, proper line termination, time skew, speed of open collector driver lines, power consumption.

- 3.3.2 Front End: Termination hardware on the front end is located on any of the following three modules: Timing Generator M8330, Major Register Control M8310 or Major Register M8300. Most of the clamp diodes required are contained in IC gates. Note that all these boards have to be installed at the front end of the Omnibus (refer to Bus Priority List A-SP-PDP8/E-Ø-4).

- 3.3.3 Tail End: All the required termination hardware for the tail end is contained on the Bus Load board M8320. Note that this board has to be installed always in the last slot of the OMNIBUS for any given bus length or system configuration.

- 8 -

3.4 Drivers and Driving Capability

3.4.1 Driver Types:

| Driver<br>Type | Location on<br>Omnibus | Group<br>Used | Circuit<br>Used                   | Notes                       |

|----------------|------------------------|---------------|-----------------------------------|-----------------------------|

| 1              | Anywhere               | 1             | DEC 8881<br>DEC 97401<br>DEC 8235 |                             |

|                |                        | 2             | DEC 8881                          |                             |

|                |                        | 3             | DEC 8881<br>DEC 97401<br>DEC 8235 |                             |

| 2              | Front end only         | 4             | DEC 74H40<br>DEC 7440             |                             |

| 3              | Front end only         | 5             | DEC 74H40                         |                             |

| 4              | Anywhere               | 6             | DEC 8881                          | 2 Circuits in parallel      |

| 5              | Anywhere               | 7             | DEC 3009                          | Emitter follower<br>pull-up |

3.4.2 Driving Capability (Operating range  $0^{\circ}\text{C}$  to  $55^{\circ}\text{C}$ )

| Circuit   | Driving Capability /                            | Leakage Respect.<br>High State                      | Notes |

|-----------|-------------------------------------------------|-----------------------------------------------------|-------|

| DEC 8881  | 16 mA at 0.4V<br>50 mA at 0.8V                  | -25 uA at 3.5V                                      |       |

| DEC 8235  | 16 mA at 0.4V<br>16 mA at 0.4V<br>48 mA at 0.4V | -25 uA at 5.5V<br>-25 uA at 3.5V<br>-1.2 mA at 2.4V |       |

| DEC 74H40 | 60mA at 0.4V                                    | -1.5 mA at 2.4V                                     |       |

| DEC 3009  |                                                 | -40 mA at 3.5V                                      |       |

|           |                                                 |                                                     |       |

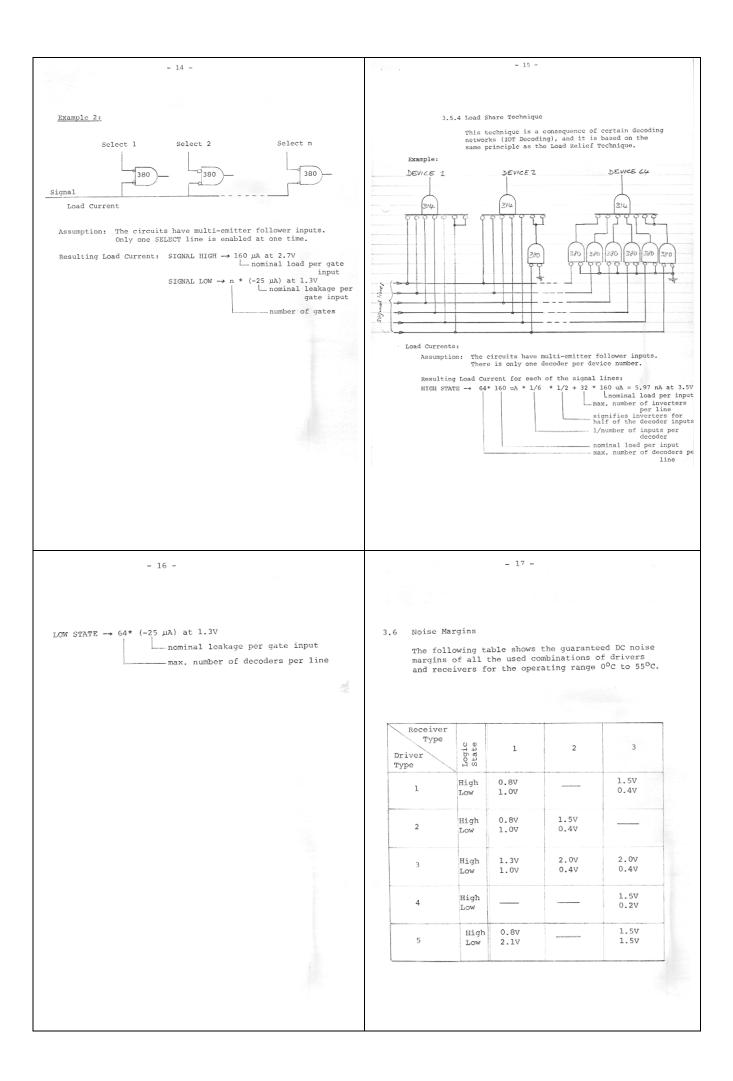

## 3.5 Receivers and Loading Characteristic

## 3.5.1 Receiver Types

| Receiver<br>Type | Locations on<br>OMNIBUS | Group<br>Used | Circuit Used                                                                                                  | Notes                                                                   |

|------------------|-------------------------|---------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1                | Anywhere                | 1,3,5,7       | DEC 314, 6314, 5314,<br>7314<br>DEC 380, 6380, 5380,<br>7380<br>DEC 384, 5384, 7384                           |                                                                         |

|                  |                         | 2,4           | DEC 314, 6314<br>DEC 380, 6380<br>DEC 384                                                                     |                                                                         |

| 2                | Anywhere                | 4,5           | Any of the DEC 74XX<br>or DEC 74HXX Series<br>circuits with 2-input-<br>minimum positive AND<br>or NAND gate. |                                                                         |

| 3                | Front end<br>only       | 1,2,3,5       | Any of the DEC 74XX,<br>DEC 74HXX or DEC 74LXX<br>series circuits.                                            | This type is<br>not standard,<br>refer to<br>3.5.3 for<br>more details. |

Receiver Type 1: This type receiver, which is equivalent or similar to the UTILOGIC 300 series gates, is the only type receiver necessary for standard OMMIBUS interfacing. For economical and part procurement reasons up to four different circuits with the same logic function are in use. The proper selection of the circuit is reflected in the above table, and the specific deviations are shown in 3.5.2. table, and the specific deviations are shown in 3.5.2.

Receiver Type 2: This type receiver, which is equivalent to any standard TTL 74XX or 74HXX series 2-input-minimum positive AND or NAND gate, is used for timing signals in the memory, memory options and some other internal options. The use of this type receiver is not allowed in standard interfacing techniques upless so specified techniques unless so specified.

Receiver Type 3: This receiver type, which is equivalent to any standard TTL 74XX, 74HXX or 74LXX series circuit, is used in specific cases in the CPU and in certain internal options. The use of this type receiver is not allowed in standard interfacing techniques, since heavier loading and smaller noise margins require special consideration.

- 12 -

# 3.5.2 Loading Characteristic & Switching Speed (Operating range 0°C to 55°C)

| Circuit   Input Loading Chara |                | Characteristic |      |      | gation Delay (ns)*<br>High Going   Input Low Going |      |  |

|-------------------------------|----------------|----------------|------|------|----------------------------------------------------|------|--|

| 022 022                       | Low State      | High State     | Min. | Max. | Min.                                               | Max. |  |

| DEC 314                       | -25µA at 1.3V  | 160uA at 2.5V  | 10   | 35   | 10                                                 | 45   |  |

| DEC5314                       |                | 160uA at 2.7V  | 0    | 35   | 0                                                  | 45   |  |

| DEC6314                       |                |                | 10   | 35   | 10                                                 | 45   |  |

| DEC7314                       |                |                | 0    | 36   | 0                                                  | 18   |  |

| DEC 380                       | -25µA at 1.3V  | 160uA at 2.5V  | 10   | 35   | 10                                                 | 45   |  |

| DEC5380                       |                | 160uA at 2.7V  | 0    | 35   | 0                                                  | 45   |  |

| DEC6380                       |                |                | 10   | 35   | 10                                                 | 45   |  |

| DEC7380                       |                |                | 0    | 36_  | 0                                                  | 18   |  |

| DEC 384                       | -25µA at 1.3V  | 160uA at 2.7V  | 10   | 45   | 10                                                 | 35   |  |

| DEC5384                       |                |                | 0    | 45   | 0                                                  | 35   |  |

| DEC7384                       |                |                | 0    | 26   | 0                                                  | 20   |  |

| DEC 74 .                      | 1.6mA at 0.4%  | 40uA at 2.4V   | 0    | 15   | 0                                                  | 29   |  |

| DEC 74H.                      | 2.0mA at 0.4   | 7 50uA at 2.4V | 0    | 10   | 0                                                  | 10   |  |

| DEC 74L                       | 0.18mA at 0.3V | 10uA at 2.4V   | 0    | 60   | 0                                                  | 60   |  |

<sup>\*</sup>For the indicated propagation delay the capacitive load at the output is 15 pF on all circuits except the DEC 74HXX (25 pF) and the DEC 74LXX (50 pF).

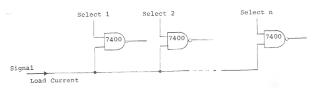

# 3.5.3 Load Relief Technique

The essence of this technique is that the option, device or field select network provides the "hold off" current for a receiver to relieve bus loading. This technique is commonly used in OMNIBUS interfacing.

## Example 1

Assumption: The circuits have multi-emitter inputs.

Only one SELECT line is enabled at one time.

Resulting Load Current: SIGNAL LOW  $\rightarrow$  -1.6 mA at 0.4V L nominal load per gate input

number of gates

#### 4. Timing Considerations

# 4.1 Rise and Fall Times

The rise and fall times are a function of the length of the OMNIBUS and the loading. The rise time of all Open Collector signal lines is particularly dependent on this property.

Definition of Rise Time:

## Table:

| Group | Typical Ris | e Time for Va | rious Length | OMNIBUS | Notes         |

|-------|-------------|---------------|--------------|---------|---------------|

| -     |             | TII(ns)       |              |         |               |

| 1     | 30          | 50            | 150          | 180     |               |

| 2     | 10          | 20            | 50           | 60      | Fast speed up |

| 3     | 15          | 25            | 75           | 90      | Slow speed up |

#### 4.2 Propagation Delay

The propagation delay is a function of the length of the OMNIBUS and the loading. Typical delay times are listed in 2.2. The OMNIBUS PRIORITY LIST (A-SP-DDB/E-0-4) defines the proper module assignments on the bus in order to avoid conflicts or unnecessary losses of time margins due to "Round Trip" delays. Unless an option fits into one of the listed categories on the Priority List, a careful timing analysis is required and the list has to get updated accordingly.

The maximum time skew between any of the OMNIBUS lines due to different line characteristics is 20 ns for the maximum length OMNIBUS provided none of the loading rules are violated.

- 20 -

## Crosstalk

# 5.1 Crosstalk on OMNIBUS

Crosstalk is an inherent problem to the OMNIBUS. Given the electrostatic and magnetic coupling between edge runs and connector pins and the typical rise and fall times of state of the art circuitry, a significant amount of crosstalk becomes a fact of life.

Solutions which would eliminate the source of such problems are not feasible under the circumstances. Typically the crosstalk is worst for signal lines which are surrounded by a number of simultaneously switching lines. In order to circumvent this problem a number of techniques have been systematically applied in the design of the PDP8/E system.

## 5.2 Techniques to Avoid Crosstalk Problems

## 5.2.1 Optimum Noise Margins

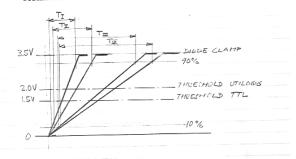

The driver-receiver combination with the optimum noise margins are used where ever it is possible (see paragraph 3.6).

# 5.2.2 Integration

Signal lines carrying register information during the whole machine cycle (MA lines, etc.) are buffered by receivers with a specified minimum propagation delay time. The integrating effect of such gates filters out some of the very fast noise spikes.

## 5.2.3 Edge Triggered Clocking

Information loaded from the OMNIBUS to any type register is done by means of edge triggering. One reason is to prevent flip-flops from being vulnerable to noise during the duration of clock pulses. Secondly, on bidirectional lines logic conflicts could occur. Typical example:

- 21 -

In an output transfer with Clear the AC, supposedly asserted DATA lines can change state during the clock pulse (TP3), causing wrong information being loaded into non-edge triggered registers.

## 5.2.4 Skewing

The clocking in the system is done at times where bus lines, adders, logic trees, etc., have settled.

# 5.2.5 Conditional Enabling

In some cases the enabling of receivers is restricted to certain periods of the machine cycle or to certain events in order to reduce vulnerability to noise.

Example: STROBE and INHIBIT are gated with FIELD and WRITE in a memory system. The MD lines in peripherals are gated with I/O PAUSE.