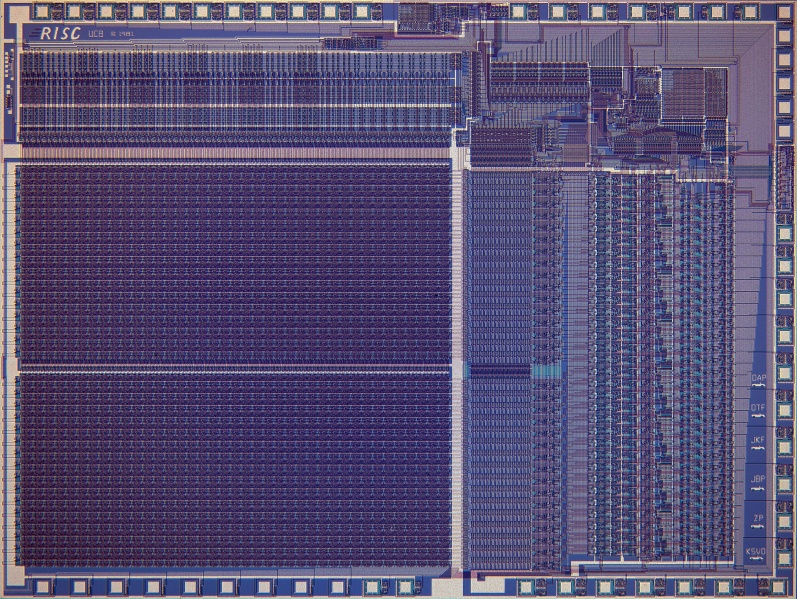

File:RISC1.jpeg

From ETHW

Size of this preview: 797 × 599 pixels. Other resolution: 2,154 × 1,620 pixels.

Original file (2,154 × 1,620 pixels, file size: 1.95 MB, MIME type: image/jpeg)

RISC-I chip, die area 77 mm2, includes 44,420 transistors. Small block at upper right is the central processing unit, implementing 31 instructions. Lower left block is a register file of 78 dual-port 32-bit registers. Blocks at top left and lower right provide selective access to the registers for reading and writing. Technology employed was metal-gate NMOS with a minimum feature size of 5 micrometers.

Dave&Carlo.jpg

RISC1group.jpg

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

| current | 18:18, 5 June 2013 |  | 2,154 × 1,620 (1.95 MB) | Dahodges (talk | contribs) | RISC-I chip, die area 77 mm2, includes 44,420 transistors. Small block at upper right is the central processing unit, implementing 31 instructions. Lower left block is a register file of 78 dual-port 32-bit registers. Blocks at top left and lower right |

You cannot overwrite this file.

File usage

The following page uses this file: